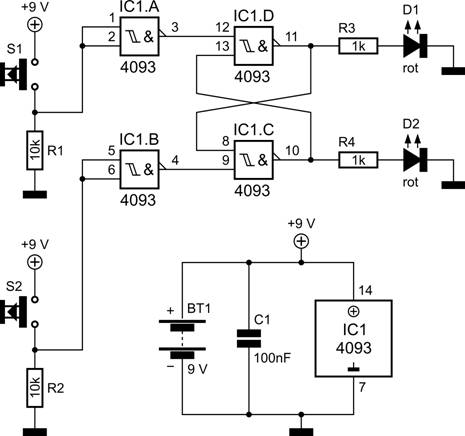

4.2 RS-Flipflop mit NAND-Gattern

Ein RS-Flipflop kann auch mit zwei NAND-Gattern aufgebaut werden. Allerdings ist dann der stabile Ruhezustand durch 1-Zustände an den NAND-Eingängen gekennzeichnet. Will man dagegen den normalen Ruhepegel 0 verwenden müssen die Eingänge zunächst invertiert werden. Dafür werden die beiden freien NAND-Gatter des 4093 verwendet.

Bild 4.3: RS-Flipflop aus NOR-Gattern

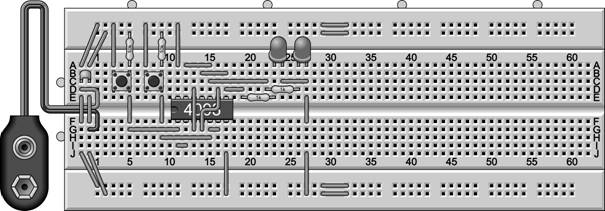

Bild 4.4: RS-Flipflop mit 4093

Tabelle 4.2: Das RS-Flipflop

|

Eingang 1, S1 |

Eingang 2, S2 |

Ausgang 1, D1 |

Ausgang 2, D2 |

|

0 |

0 |

x |

x |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

Die Wahrheitstabelle entspricht in der grundlegenden Funktion der im vorigen Abschnitt. Wenn allerdings beide Eingänge gleichzeitig gesetzt werden sind diesmal beide Ausgänge ebenfalls 1.

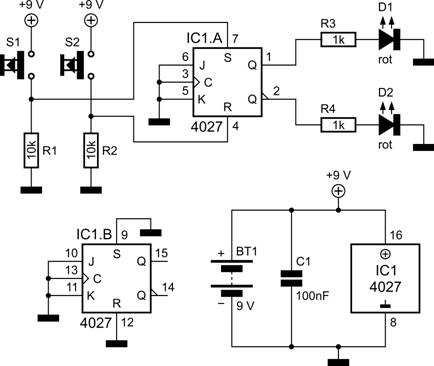

4.3 JK-Flipflop als RS-Flipflop

Flipflops kann man nicht nur aus einzelnen Gattern zusammensetzen sondern man erhält sie auch als komplexe Bausteine, die intern bereits viele Gatter enthalten. Es gibt zahlreiche unterschiedliche Typen, darunter das RS-Flipflop und das JK-Flipflop. Der 4027 enthält zwei flankengetriggerte JK-Flipflops mit zusätzlichen R und S-Eingängen. Was es mit den Eingängen J und K sowie C auf sich hat wird im folgenden Abschnitt erläutert. Legt man sie an GND, dann verhält sich der Baustein wie ein normales RS-Flipflop. Der Ausgang Q wird mit einem 1-Pegel an S auf 1 gesetzt und mit einem 1-Pegel an R zurückgesetzt. Der zweite Ausgang /Q ist jeweils zum Q-Ausgang invertiert. Setzt man aber beide Eingänge dann verhält sich der 4027 wie das RS-Flipflop aus NAND-Gattern im vorigen Abschnitt, d.h. Q und /Q sind 1.

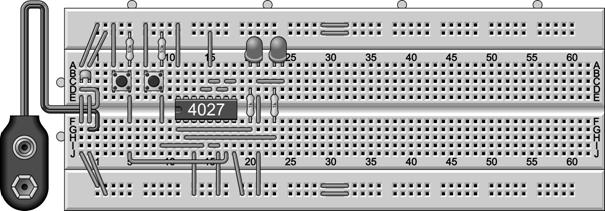

Bild 4.5: RS-Flipflop mit dem 4027

Bild 4.6: Das 4027-Flipflop

Tabelle 4.3: Das RS-Flipflop im 4027

|

Eingang S, S1 |

Eingang R, S2 |

Ausgang Q, D1 |

Ausgang /Q, D2 |

|

0 |

0 |

x |

x |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |